Predicting Final Test outcomes to reduce operational costs

In the fast-paced world of semiconductor manufacturing, achieving higher yields and reducing costs are constant challenges. Ideally, yield should only be impacted by unavoidable defects when everything else is performing as expected. However, when yield reduction occurs due to the process sensitivity of the design, these issues can be detected and, in many cases, corrected.

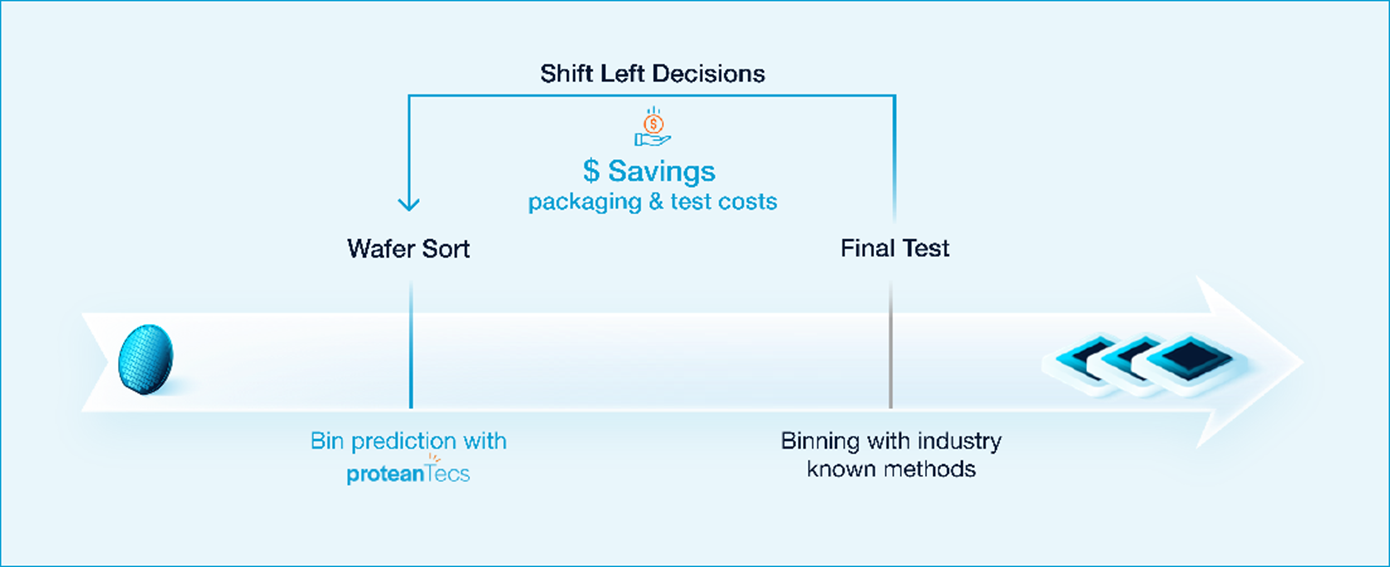

proteanTecs has developed a cloud-based application that correlates failing bins within production testing stages using deep data monitoring agents, in addition to an edge application to allow decision-making during ATE testing. When a correlation is found, an alert is sent to the customer. While improving the design process sensitivity is the preferable solution to address this yield loss, in some cases, such a design tune is not possible or too complicated to achieve. In these cases, another immediate and effective strategy is to implement a “shift-left” approach. By disqualifying problematic chips as early as possible in the production testing process, manufacturers can significantly reduce costs—especially when failures are identified during the packaged device testing stage, and even more so when packages include multiple chiplets where the cost of late disqualification is substantial.

This blog explores how proteanTecs’ shift-left solution leverages deep data from early stages, such as Wafer Sort, and applies advanced machine learning techniques to predict Wafer Sort failing bins and even Final Test failing bins with remarkable accuracy. By identifying and addressing potential issues earlier in the production testing process, semiconductor manufacturers can save costs in packaging, testing, and overall yield optimization.

The Shift-Left Approach: Moving Issue Detection Upstream

Traditionally, semiconductor manufacturing has relied on final testing as a critical step to determine the quality and functionality of chips. However, this approach can lead to significant waste, as chips that fail the final test have already undergone expensive packaging and other processes.

The shift-left strategy aims to detect potential failures earlier in the production process, ideally during wafer sort, to prevent such losses.

The costs associated with failing chips are not limited to packaging alone. Additional costs include test time, burn-in testing, and system-level testing. Chips that fail during final testing have already consumed valuable resources in these areas, making early detection even more critical for cost savings.

Furthermore, as the semiconductor industry shifts toward more costly and complex packaging solutions, such as 2.5D/3D heterogeneous packages, these expenses become increasingly significant. Consequently, the potential for cost savings grows even more critical.

Predicting Soft (Failing) Bins with On-Chip Monitoring and Machine Learning

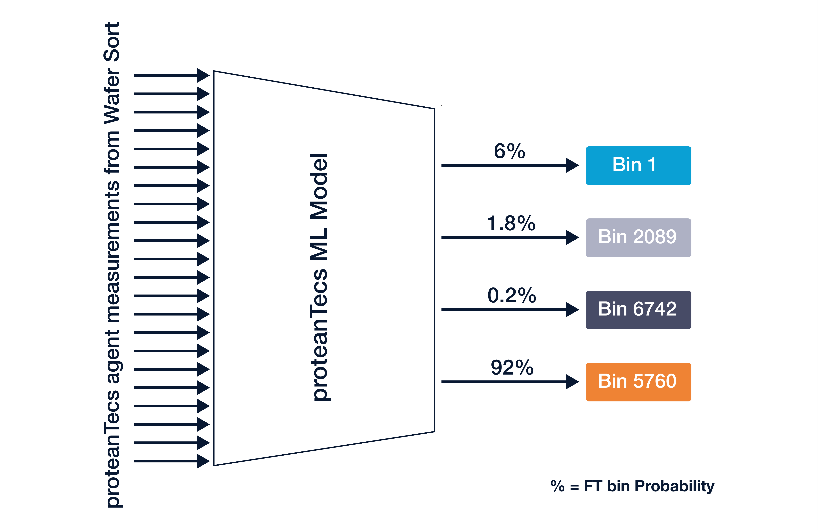

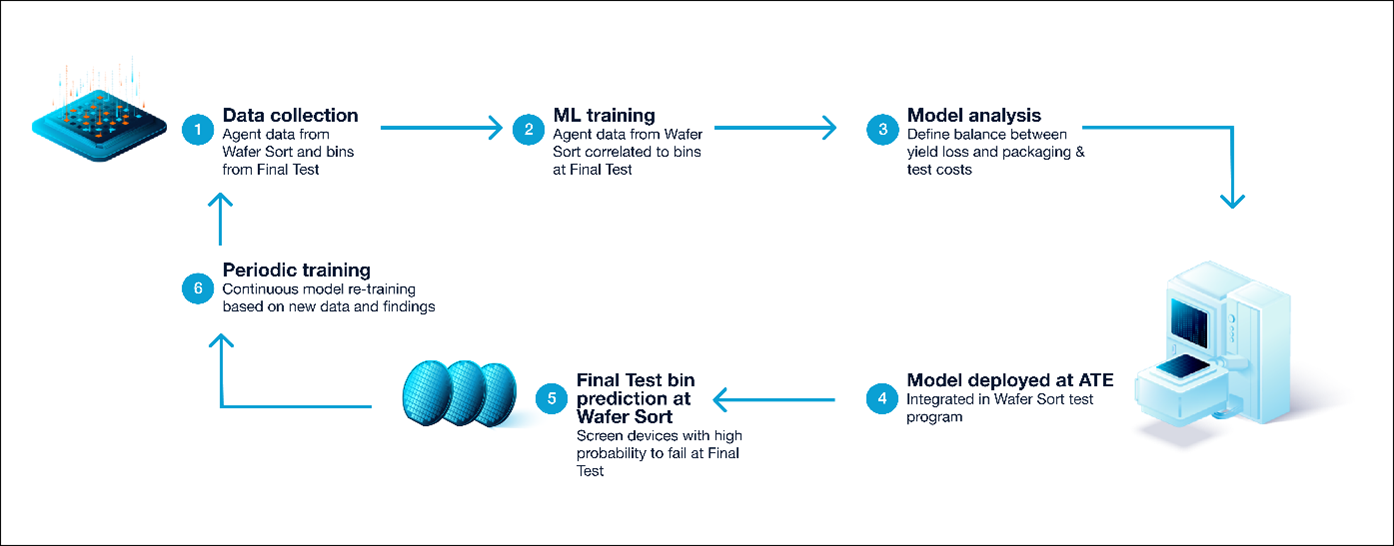

This is where proteanTecs deep data analytics come into play. Based on parametric measurement of on-chip agents, proteanTecs provides advanced analytics during semiconductor production testing. These agents collect detailed profiling data during the wafer sort process, capturing the process variation on the related transistor types and the standard cells most frequently used by the customer. By applying machine learning algorithms to the wafer sort data, it is possible to predict the likelihood that a chip will fall into a specific bin during the final test, specifically, potentially failing bins.

The model is trained on the proteanTecs cloud platform, and once optimized, the trained model is downloaded to the tester using the proteanTecs edge library, allowing for seamless integration into the manufacturing process.

proteanTecs shift-left ML flow

To learn more about proteanTecs deep data technology, download the proteanTecs On-Chip Monitoring and Deep Data Analytics System white paper here.

Cost Savings Through Early Detection

In semiconductor testing, “soft (failing) bins” refer to sub-categories of test results. More specifically, the higher granular reason of a failure or the inability to fully meet the required specifications. Understanding which chips are likely to fall into specific soft bins can be incredibly valuable for manufacturers, as it allows for more informed decision-making regarding packaging and further testing.

One of the most significant advantages of using proteanTecs’ shift-left solution is the potential for substantial cost savings. By predicting which chips are likely to fail or fall into specific soft bins during wafer sort, manufacturers can avoid unnecessary packaging and testing costs. Chips that are predicted to fail can be scrapped or reworked before additional resources are invested in them.

Beyond packaging, these costs can include test program development, burn-in testing, and even system-level testing, all of which contribute to the overall expense. Early detection through proteanTecs’ solution allows for significant reductions in these costs, enhancing the overall efficiency of the manufacturing process.

Moreover, this predictive capability allows for better yield management. If a high percentage of chips are predicted to fall into a failing bin, it could indicate design sensitivities to manufacturing process that needs to be addressed. By identifying such trends early, manufacturers can make adjustments to the design, potentially improving overall yield and reducing the number of defective chips.

Feature Importance and Process Optimization

Another powerful aspect of proteanTecs’ solution is the ability of the machine learning algorithms to output feature importance and profile each die within the full population. Feature importance indicates which parameters or characteristics of the chips are most influential in predicting the final test outcome. Since the proteanTecs agents measure various aspects of the design and manufacturing process, this information can be used for production optimization.

For example, if the model shows higher correlation of the failed bin to a specific Vt, manufacturers can investigate and adjust these parameters to improve outcomes. This not only enhances yield but also contributes to a more robust and reliable manufacturing process.

Customer Case Study

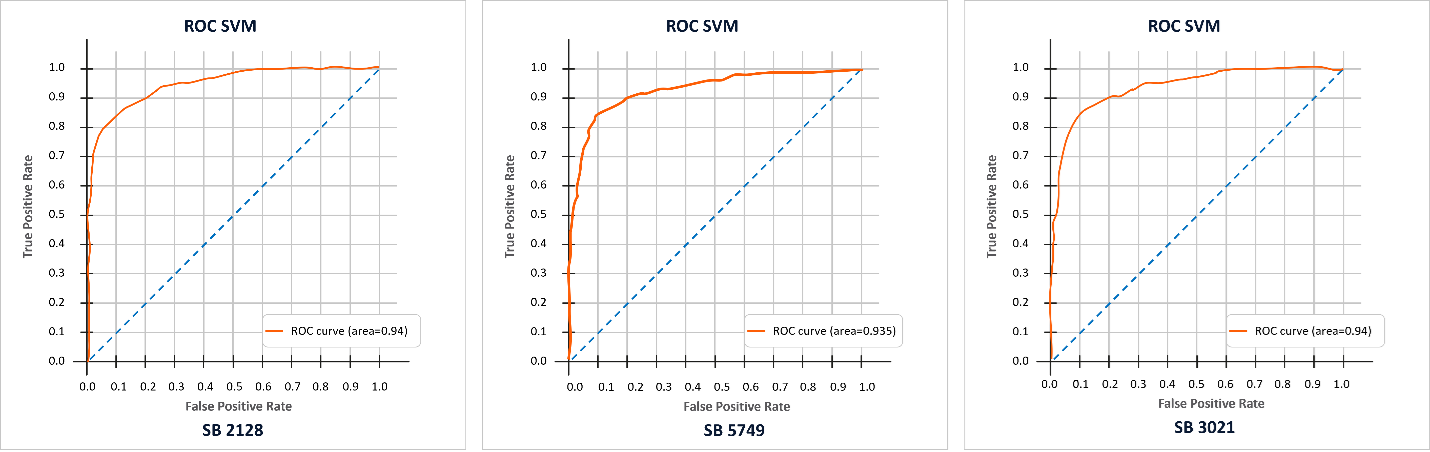

The example below showcases proteanTecs’ shift-left application running during manufacturing testing of a 5nm datacenter compute chip. The ROC (Receiver Operating Characteristic) curves presented in the images showcase the performance of a machine learning model in predicting two specific soft bins: SB 2128, SB 5749, and SB 3021. The ROC curve is a graphical representation of a model’s diagnostic ability, specifically illustrating the tradeoff between false positives (devices marked as bin Pass in final test, but the model marked them as Fail) and true positives (devices labeled as a specific failing soft bin in final test, which were indeed correctly marked as this bin by the model). The area under the curve (AUC) indicates the overall performance. In these cases, the AUC values of 0.94 and 0.935 demonstrate the model’s strong capability in distinguishing chips likely to end up in these bins.

In the case of SB 2128, the model was able to identify 50% of the chips that would later be categorized into this bin, already during the wafer sort stage itself. This early detection is crucial because it allows manufacturers to make proactive decisions, such as redirecting these chips to different processes, modifying packaging plans, or even optimizing the manufacturing process to reduce the occurrence of chips in this soft bin.

Conclusion: A Smarter Approach to Semiconductor Manufacturing

The integration of proteanTecs’ on-chip agents with machine learning models represents a significant advancement in the semiconductor manufacturing industry. By enabling a shift-left strategy, manufacturers can predict final test outcomes earlier in the production process, leading to substantial cost savings, improved yield, and a more optimized manufacturing process.

As semiconductor technology continues to evolve, the ability to predict and prevent failures earlier in the process will become increasingly critical. With proteanTecs’ innovative solutions, the future of semiconductor manufacturing is not just about making chips—it’s about making them smarter, more efficiently, and with greater precision than ever before.

Want to learn more about how proteanTecs can help you achieve higher yields, reduce costs, and improve product quality, contact us here.